## Features

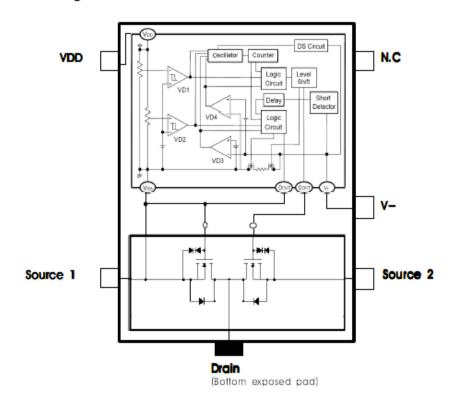

- The protection IC and The Dual- Nch MOSFET to use common Drain are integrated into One- packaging IC.

- 2. Reduced Pin- Count by fully connecting internally.

- 3. Application Part

- Protection IC

- Uses high withstand voltage CMOS process.

- The charger section can be connected up to absolute maximum rating 30V.

- ② Detection voltage precision

- Overcharge detection voltage

Overdischarge detection voltage

Discharge overcurrent detection voltage

- Charging overcurrent detection voltage

- 3 Built- in detection delay times (timer circuit)

- Overcharge detection delay time

- Overdischarge detection delay time

- Discharge overcurrent detection delay time

- Charging overcurrent detection delay time

- Short detection delay time

- 4 0V charge function is allowed

- Auto Wake- up function is not allowed

## 2) FET

- ① Using advanced trench technology to provide excellent Roscon, low gate charge and operation with gate voltage as low as 2.5V while retaining a 12V Vasawo.

- 2 The protection for ESD

- 3 Common drain configuration

- ④ General characteristics

- $V_{ps} (V) = 24V$

- $I_{n}(A) = 7A$

- $R_{SS(OM)} < 45m\Omega$  (Vas = 4.5V, In = 5A)

- ESD Rating: 2000V HBM

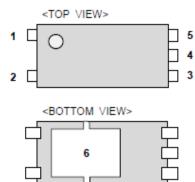

## Pin Assignment

[ Package: TEP-5L ]

| 1 | VDD                    |

|---|------------------------|

| 2 | Source 1 (same as Vss) |

| 3 | Source 2               |

| 4 | N.C (No connected)     |

| 5 | <b>V</b> -             |

| 6 | Drain                  |

## Block Diagram